<b id="0toem"><menuitem id="0toem"></menuitem></b>

<code id="0toem"><abbr id="0toem"></abbr></code>

<code id="0toem"></code>

前邊寫(xiě)了很多關(guān)于板上外圍器件的評(píng)測(cè)文章,這篇是FPGA純邏輯設(shè)計(jì),是FPGA的另一部分——算法實(shí)現(xiàn),上篇文章做了HDC1000傳感器的使用,當(dāng)時(shí)說(shuō)FPGA是不支持小數(shù)的,本篇記述的是FPGA如何去做除法運(yùn)算。很多人覺(jué)得不就是除法嘛,直接打上/即可,但是,F(xiàn)PGA是不能正確綜合這個(gè)除法器的,綜合的結(jié)果只是一個(gè)固定數(shù)值,而不像其他微處理器。可以這么說(shuō),用FPGA實(shí)現(xiàn)除法運(yùn)算是比較麻煩的。

用軟件編程的時(shí)候,用到除法器的時(shí)候,一個(gè)/就能求商,一個(gè)%就能求余,很簡(jiǎn)單。但是,如果使用硬件來(lái)實(shí)現(xiàn)除法運(yùn)算,就需要了解計(jì)算機(jī)存儲(chǔ)結(jié)構(gòu),二進(jìn)制的除法和平常使用的十進(jìn)制除法是一樣的,都是通過(guò)輾轉(zhuǎn)相除的原理,

原理如上所述,現(xiàn)在需要把這個(gè)原理轉(zhuǎn)換成可實(shí)現(xiàn)的設(shè)計(jì)方案,從圖可以看出,首先是將除數(shù)與被除數(shù)的最高3位做比較,如果除數(shù)(110)大于被除數(shù)(101),則將商賦值為0(最高位是0可以省略),被除數(shù)向右增加1位再進(jìn)行比較;當(dāng)被除數(shù)增加1位,除數(shù)(110)小于被除數(shù)(1010),則將商賦值為1,接著進(jìn)行二進(jìn)制減法運(yùn)算,被除數(shù)(1010)減去除數(shù)(110),變成100;然后被除數(shù)向右再增加1位,變成1001,再與除數(shù)(110)比較,以此類推,最后輸出結(jié)果。

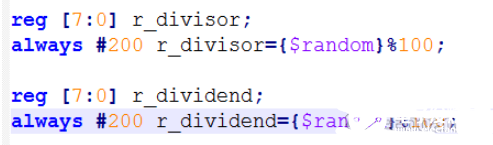

設(shè)計(jì)好代碼,用Modelsim仿真驗(yàn)證,

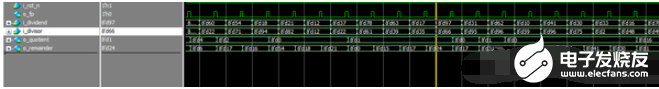

用$random產(chǎn)生隨機(jī)數(shù),實(shí)現(xiàn)效果如下:

i_dividend為被除數(shù),i_divisor為除數(shù),o_quotient為商,o_remainder為余數(shù)(下同)。

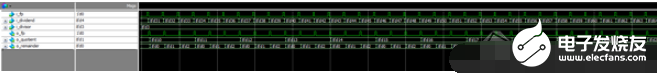

$random是不能綜合的,所以,只能用其他的進(jìn)行代替,被除數(shù)用一個(gè)計(jì)數(shù)器,除數(shù)用數(shù)字3,再進(jìn)行Modelsim仿真驗(yàn)證:

由2個(gè)圖可知,除法器設(shè)計(jì)滿足需求。

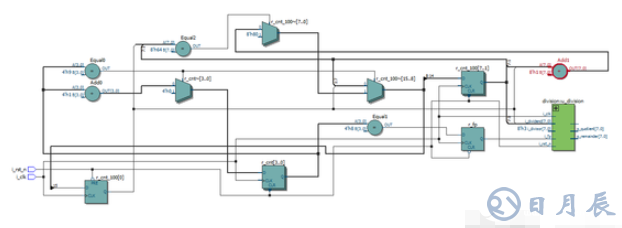

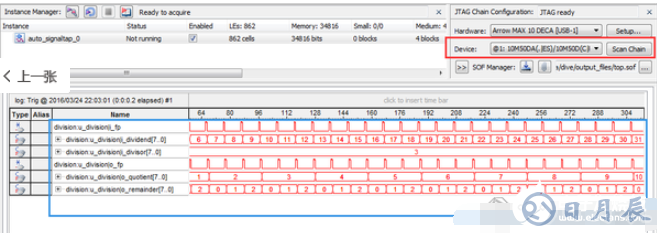

進(jìn)行板上調(diào)試,

綜合后的RTL圖,

用Quartus ii軟件查看結(jié)果,一切與預(yù)期一致,設(shè)計(jì)成功。

總結(jié):用FPGA實(shí)現(xiàn)除法器真麻煩!

<b id="0toem"><menuitem id="0toem"></menuitem></b>

<code id="0toem"><abbr id="0toem"></abbr></code>

<code id="0toem"></code>