<b id="0toem"><menuitem id="0toem"></menuitem></b>

<code id="0toem"><abbr id="0toem"></abbr></code>

<code id="0toem"></code>

Vivado FPGA設(shè)計基礎(chǔ)操作流程

當(dāng)然在介紹的過程當(dāng)中會給大家推薦一些對于工具深入使用的Xilinx官網(wǎng)資料。這里以流水燈的控制為例。

Vivado的基本使用

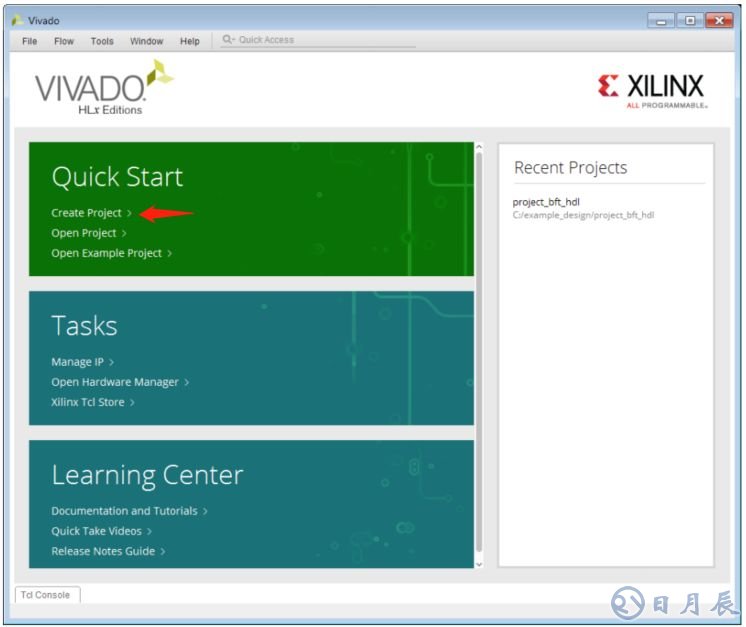

(一) 打開Vivado新建工程:

1. 安裝好Vivado之后,在Windows系統(tǒng) Start > All Programs > Xilinx Design Tools > Vivado> Vivado ,或者桌面上找到如下圖標(biāo),點擊打開Vivado。

2. 點擊Create Project

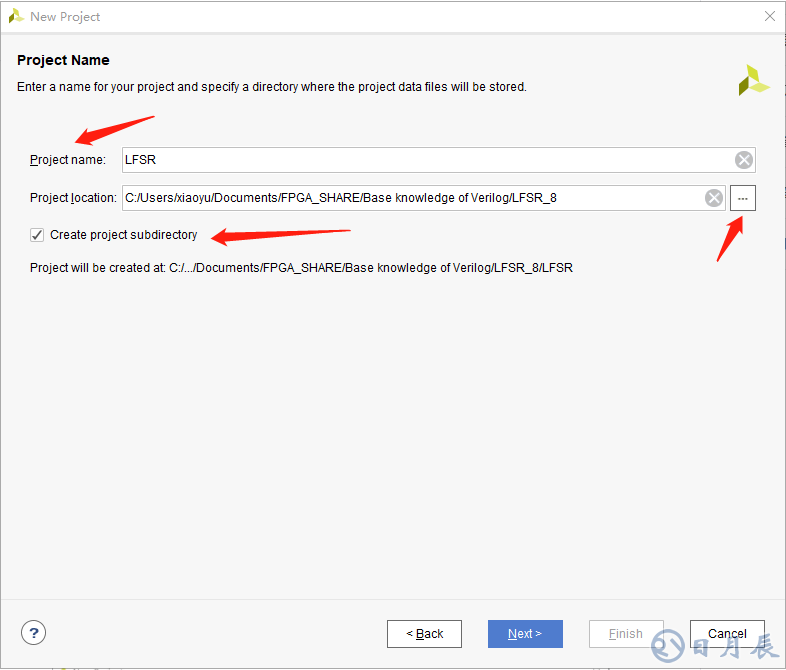

3. 指定工程所放路徑與工程名字

4. 選擇RTL Project ,此時把Do not specify at this time勾上,表示在新建工程時不去指定源文件。

5. 選擇器件或者板卡。Parts表示器件,當(dāng)然如果是板卡就點擊Boards。器件可以根據(jù)系列去選,也可以直接在Search欄搜索器件型號。器件的選擇根據(jù)你的FPGA芯片來定,一般在你所用的開發(fā)板手冊里面可以找到。選擇完畢點擊Next。

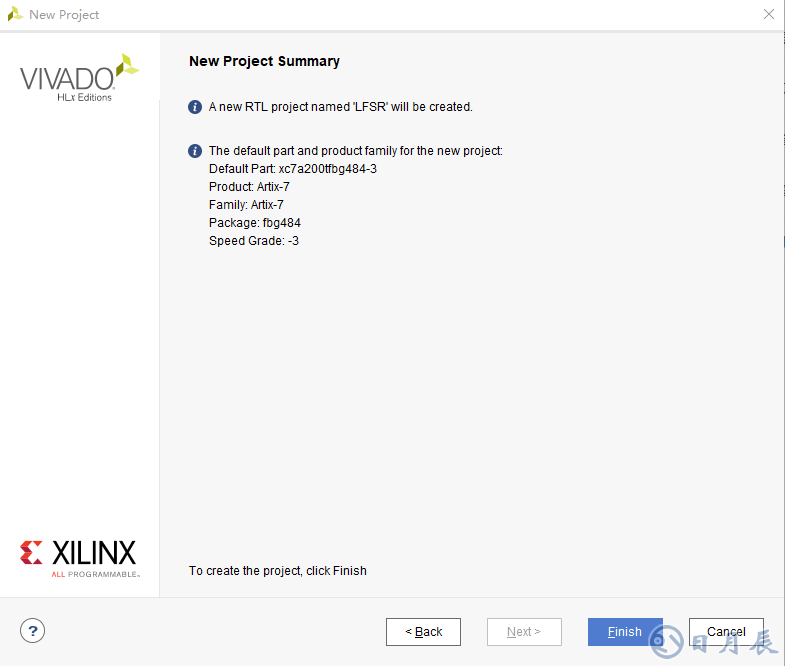

6. 確認(rèn)整個工程信息后,點擊Finish,完成工程創(chuàng)建。

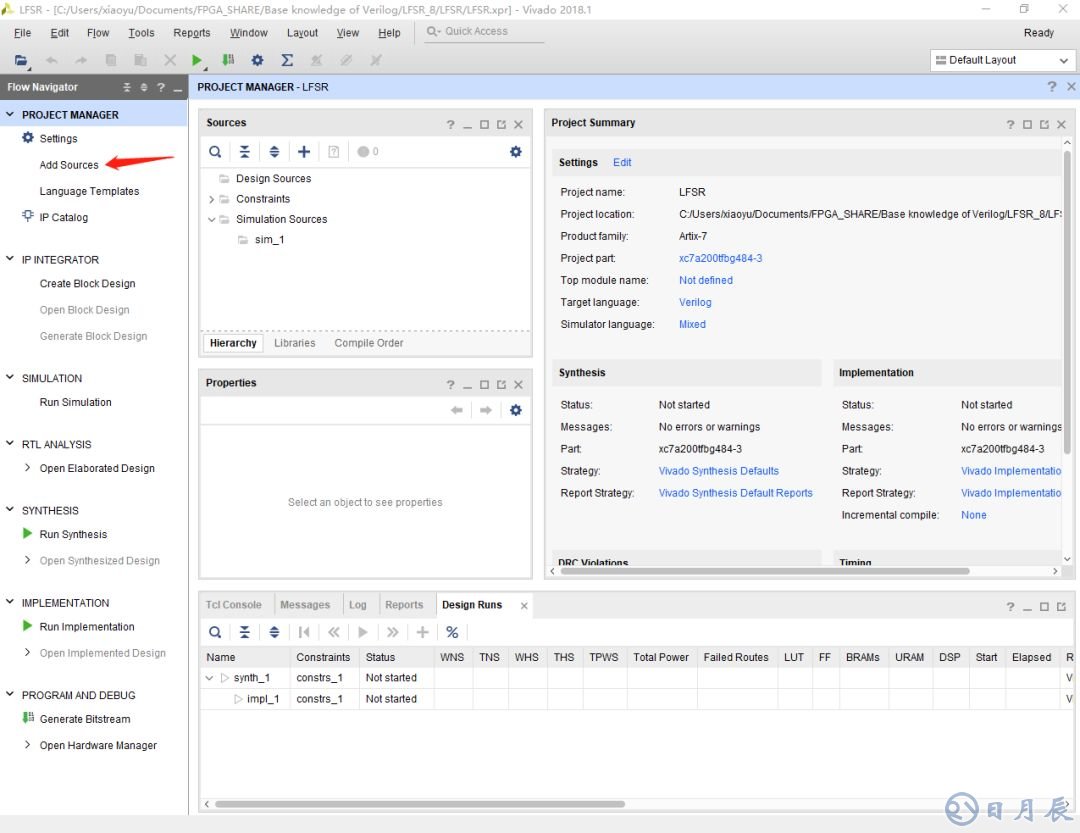

(二)新建Verilog文件:

1. 在Flow Navigator界下點擊 Add Sources.

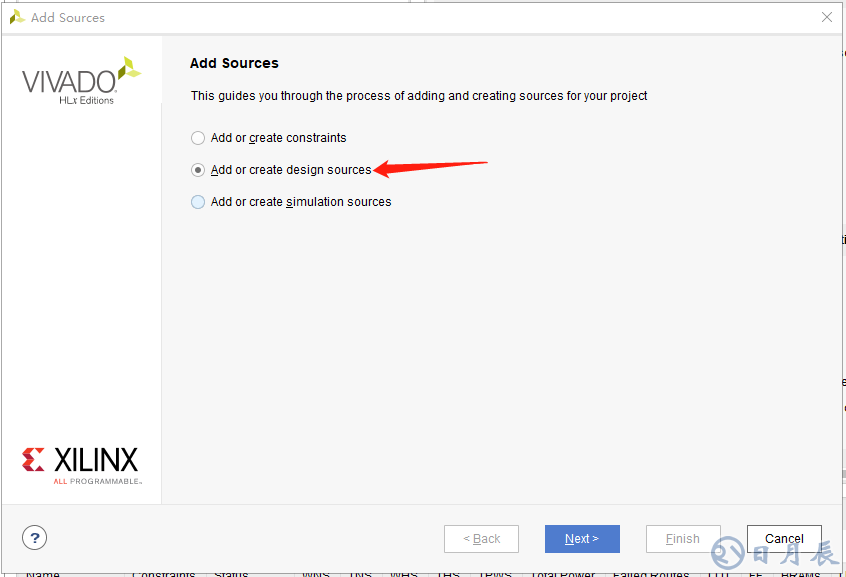

2. 如下界面,第一個是添加或者新建XDC約束文件;第二個是添加或者新建設(shè)計文件;第三個是添加或者新建仿真文件。這里選擇添加或者新建設(shè)計文件,再點擊Next。

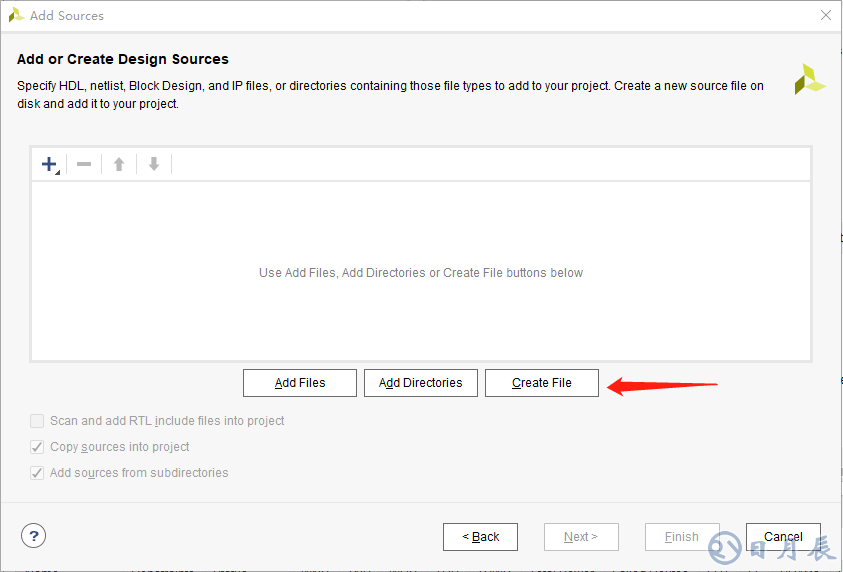

3. 這里點擊Create File。Add Files表示添加已有的設(shè)計文件,Add Directories表示添加文件夾。

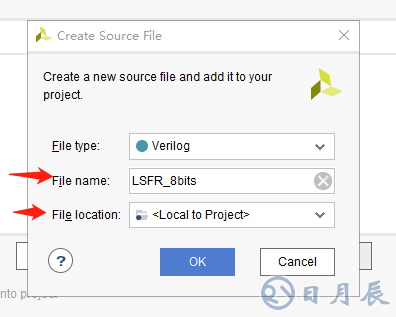

4. 指定文件名與路徑(默認(rèn)存放在工程默認(rèn)路徑),文件類型(File type)選擇為Verilog,如果你用的是其它硬件描述語言,則選擇你用的語言類型。

5. 在之后跳出的框依次點擊OK,F(xiàn)inish,Yes。這就完成了一個設(shè)計文件的新建。

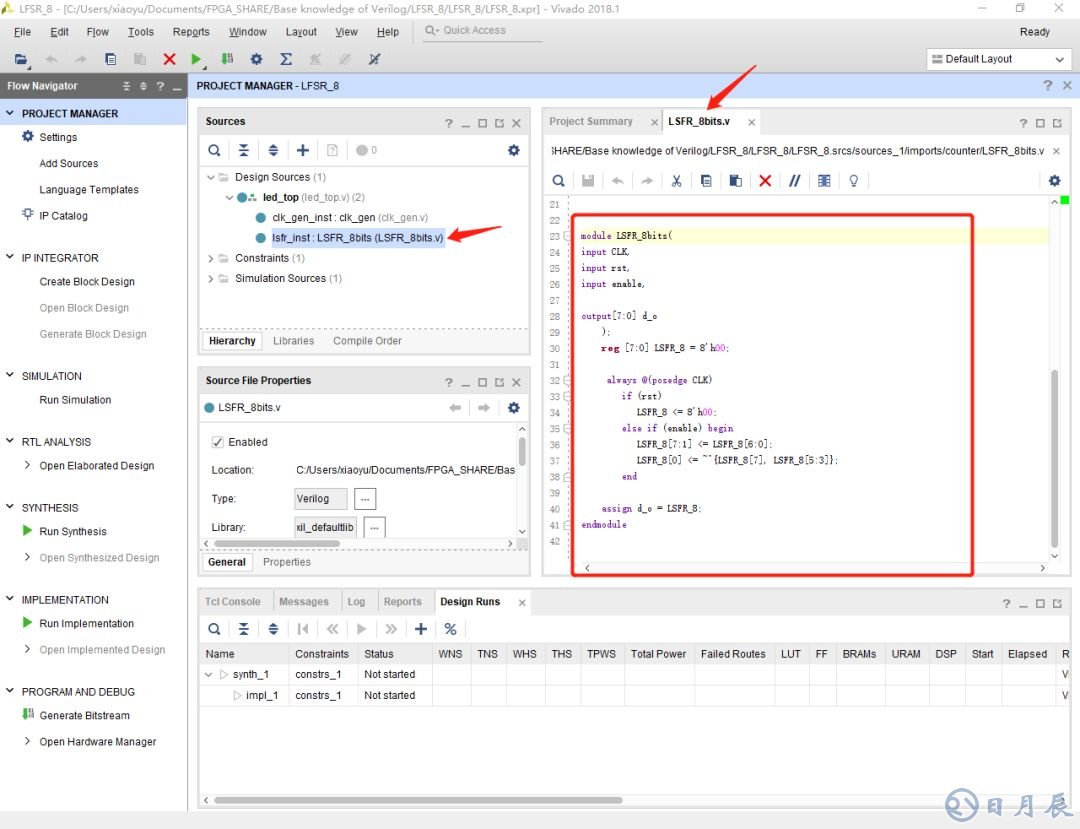

6. 在Source框雙擊剛剛新建的文件,完成你的Verilog代碼設(shè)計,并保存。

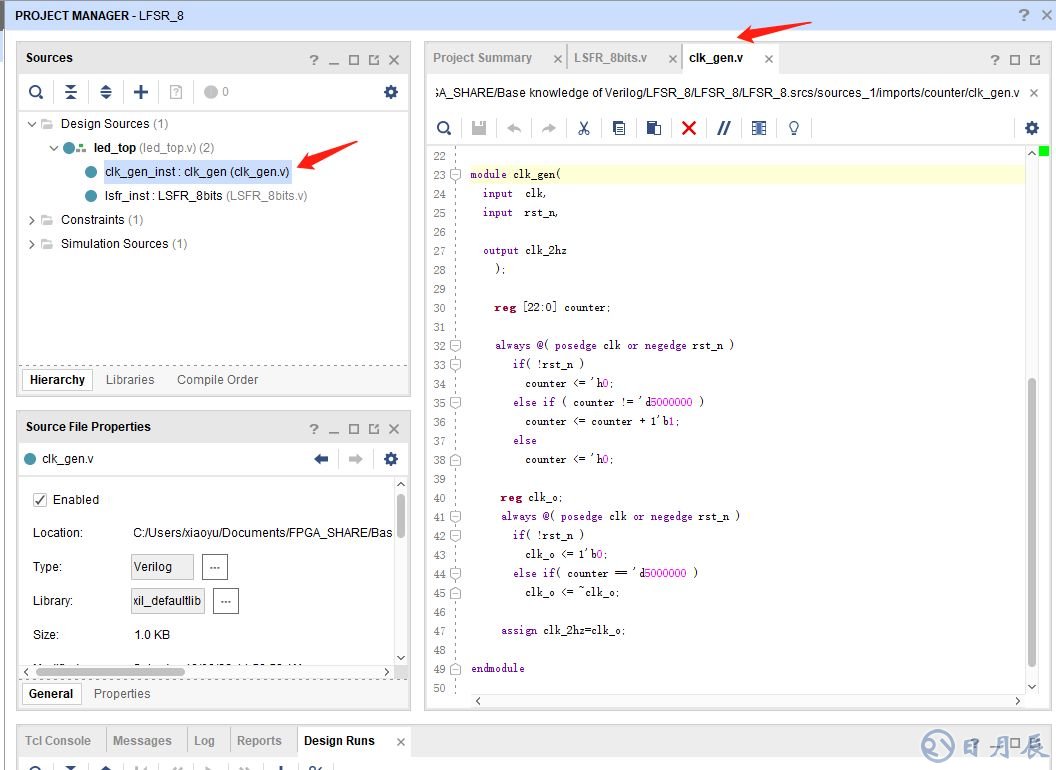

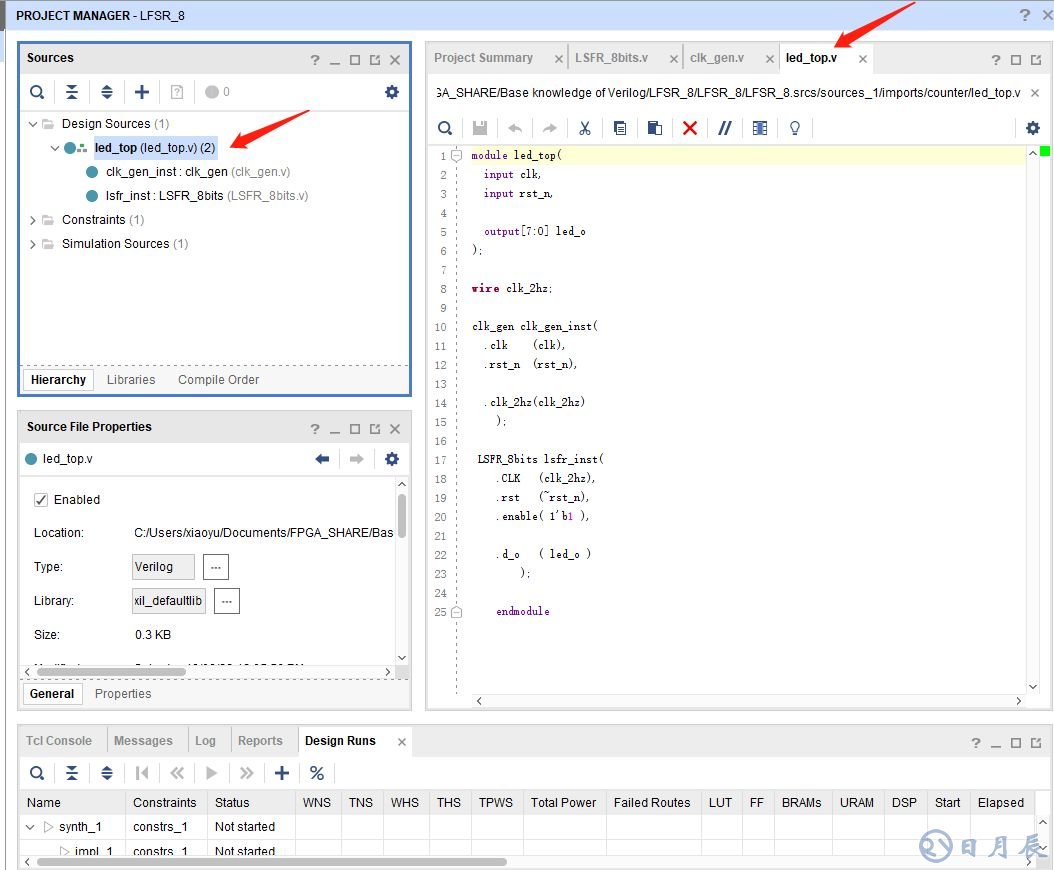

重復(fù)上述操作完成對clk_gen.v(分頻模塊)和led_top.v(頂層模塊)文件的設(shè)計與編碼。

(三) 查看 Schematic:

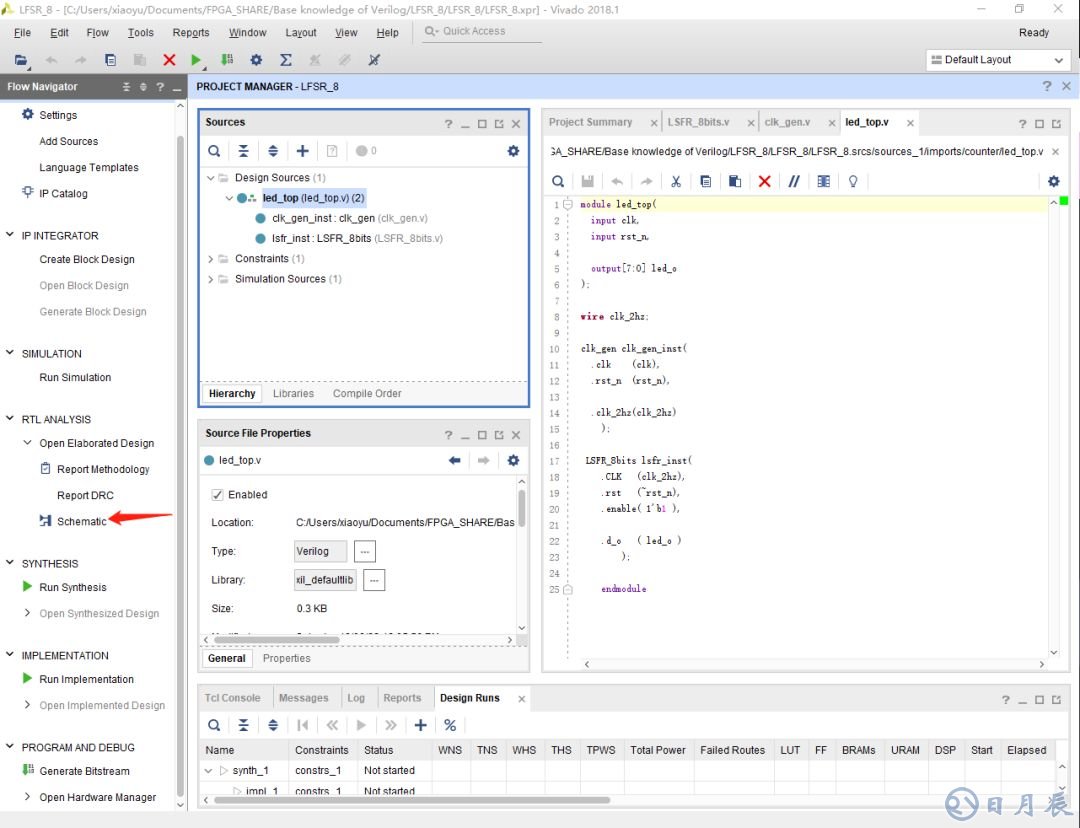

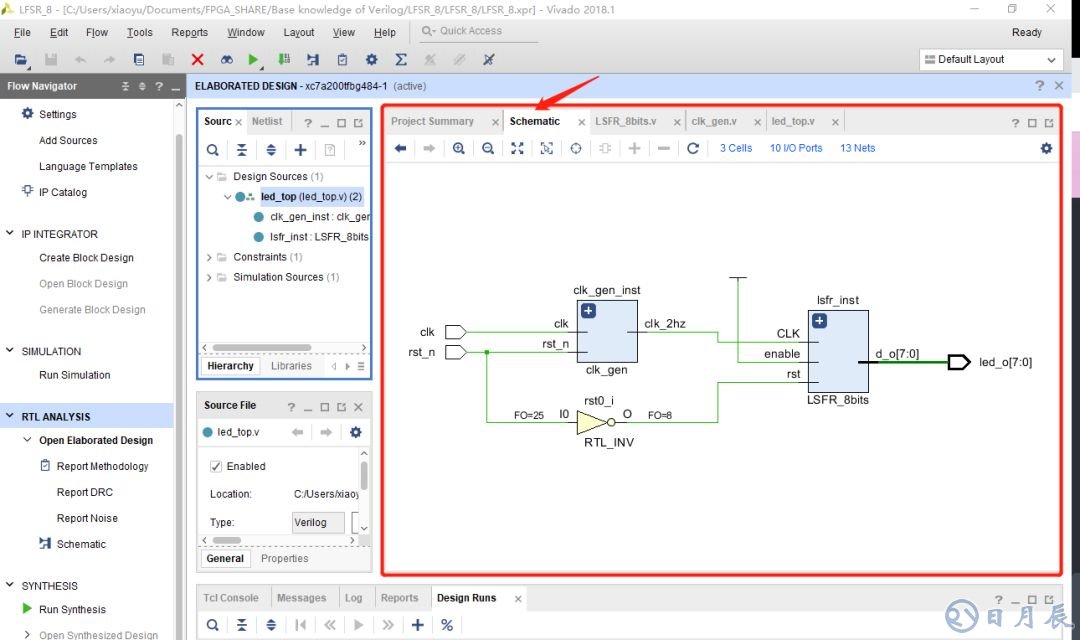

1. 在Flow Navigator 下點擊RTL ANALYSIS -> Open Elaborated Design -> Schematic

2. 一會兒就會彈出你所設(shè)計的Verilog的原理圖。點擊原理圖里模塊上的+號,可以將此模塊的內(nèi)部電路展開。

大家可以參考官網(wǎng)文檔 "Vivado Design Suite User Guide: Using the Vivado IDE (UG893)"去進(jìn)一步了解Schematic的使用。

(四)添加TB文件,做功能仿真:

在完成RTL設(shè)計之后,我們先需要對其做仿真來驗證其功能的正確性。這里先需要添加testbench文件,來給設(shè)計輸入測試激勵。

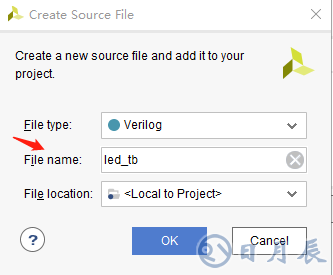

1. 添加testbench文件。在Flow Navigator界面下點擊 Add Sources -> Add or create simulation sources -> Create File,則會出現(xiàn)如下界面,選定文件名(File name),文件類型(File type)。接下來依次點擊OK,F(xiàn)inish, OK完成文件的創(chuàng)建。

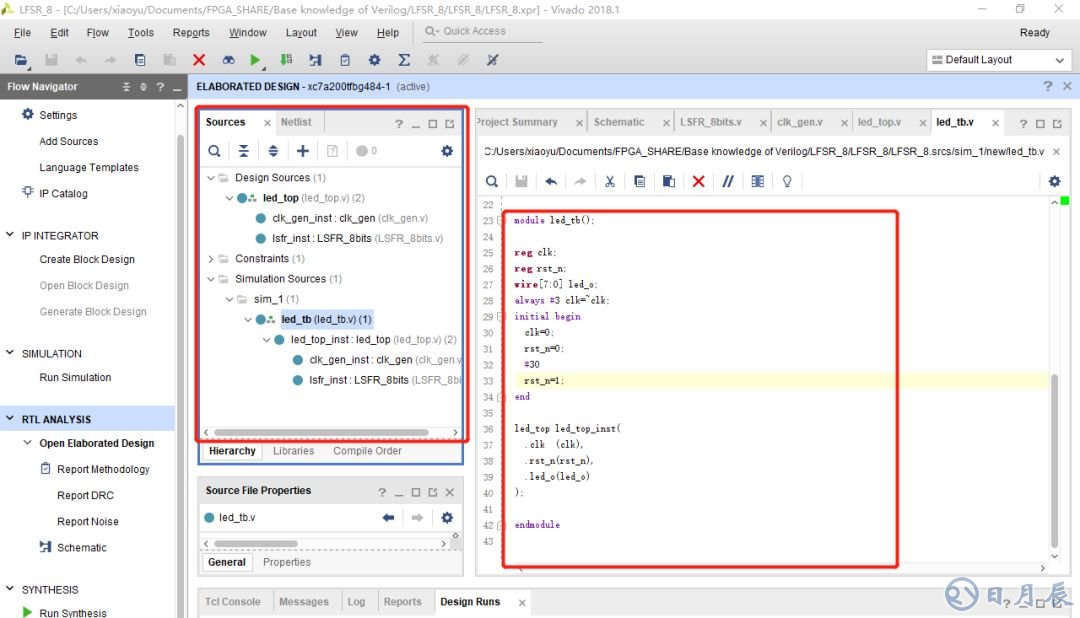

2. 在Sources框找到剛新建的tb文件,雙擊進(jìn)行編輯,完成編輯后保存。編輯完畢,則如下圖所示。

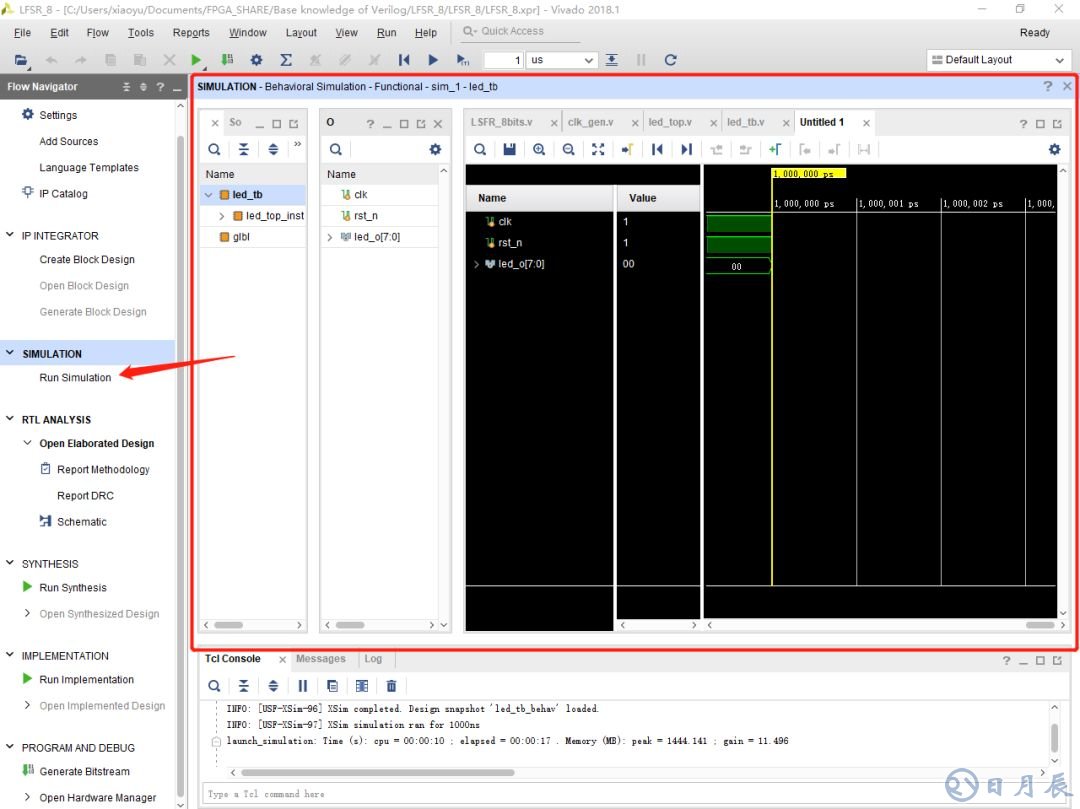

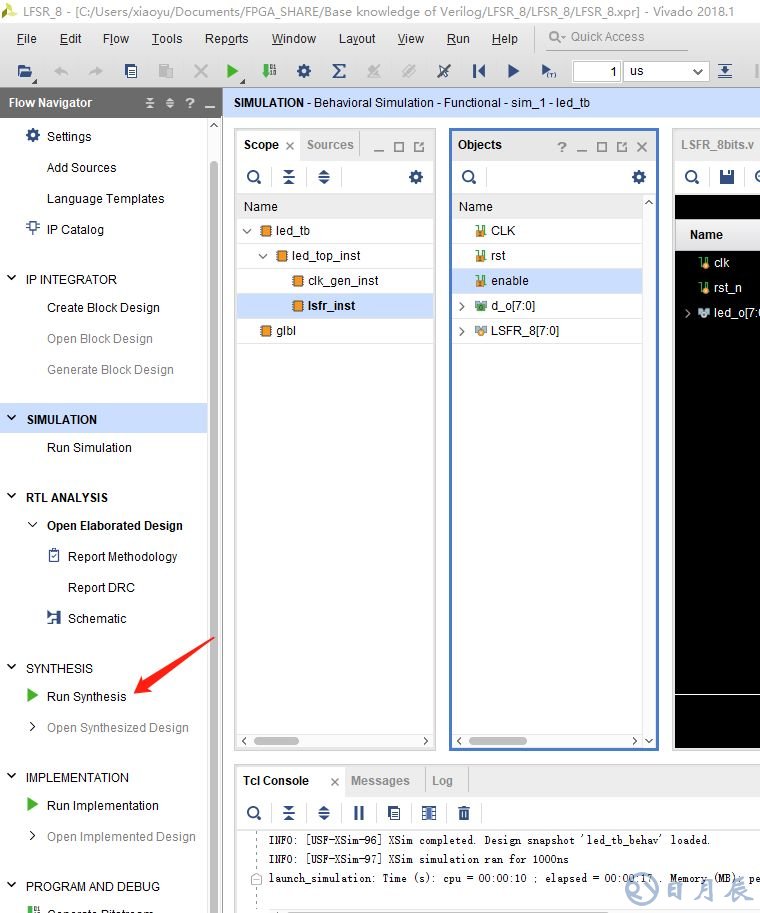

3. 在Flow Navigator界面下點擊 Run Simulation -> Run Behavioral Simultion。如果代碼沒有錯誤,則一會兒將會在右邊出現(xiàn)如下圖所示的波形窗口。

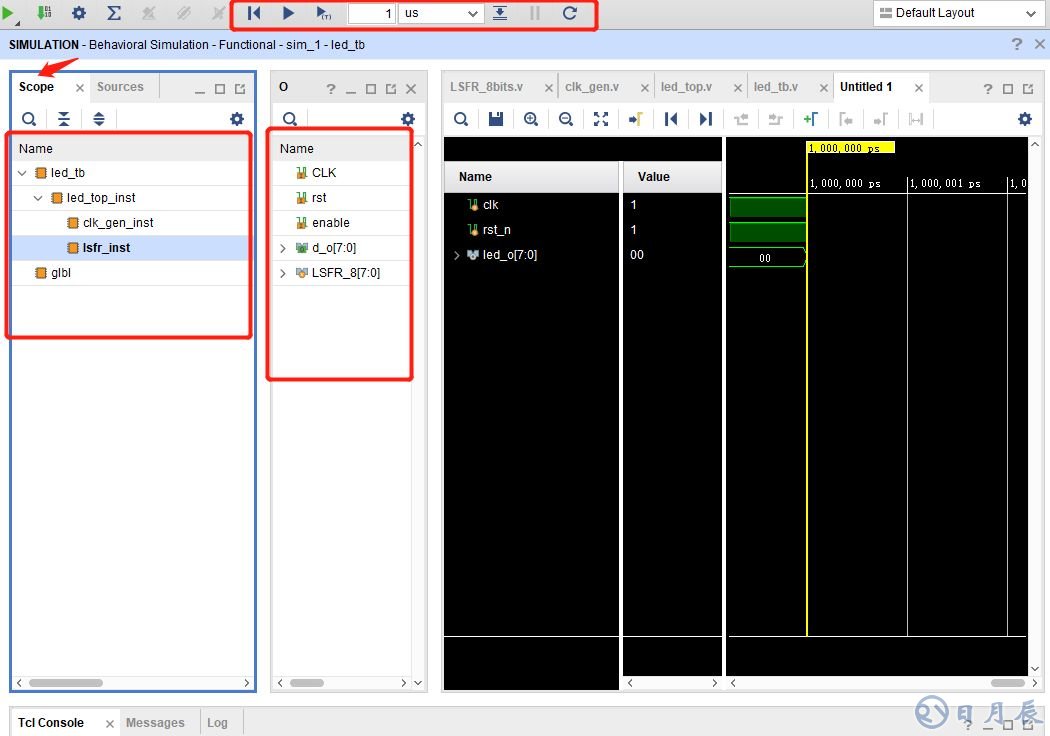

4. 在Scope框里,選擇模塊,其內(nèi)部信號顯示在其右邊的Objects框里,可以右擊選擇Add to wave window,將其添加到波形顯示窗口。界面最上方紅框框出來的幾個按鈕從最左邊到右邊三個分別是 “從新開始運行仿真”, “一直運行仿真”,“運行設(shè)定時間長度的仿真(如圖設(shè)定的時間為1us)”。每新添加信號后都需要從新運行仿真。

運行仿真是為了確認(rèn)RTL設(shè)計的功能的正確性,對于仿真的深入了解可以參閱官網(wǎng)資料“Vivado Design Suite User Guide: Logic Simulation (UG900) ” 和 “Vivado Design Suite Tutorial: Logic Simulation (UG937)”。

(六) 添加管腳約束

添加管腳約束,添加管腳約束可以選用XDC文件的方式(參考官方文檔 “Vivado Design Suite User Guide Using Constraints (UG903 )”),也可以采用界面化的方式。這里給大家介紹界面化的方式。

(五)Synthesis(綜合)

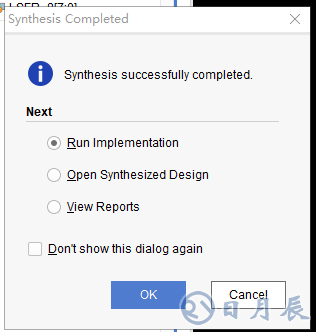

直接在Flow Navigator界面下點擊 Run Synthesis后點擊OK即可。

Synthesis完畢后就會跳出如下信息框。選擇Open Synthesized Design后點擊OK。

對于Synthesis的其它一些設(shè)置選項等等,大家可以參考官網(wǎng)文檔 “Vivado Design Suite User Guide:Synthesis (UG901)”。

(六) 添加管腳約束

添加管腳約束,添加管腳約束可以選用XDC文件的方式(參考官方文檔 “Vivado Design Suite User Guide Using Constraints (UG903 )”),也可以采用界面化的方式。這里給大家介紹界面化的方式。管腳約束是為了將設(shè)計的輸入輸出引腳映射到FPGA芯片的引腳上。

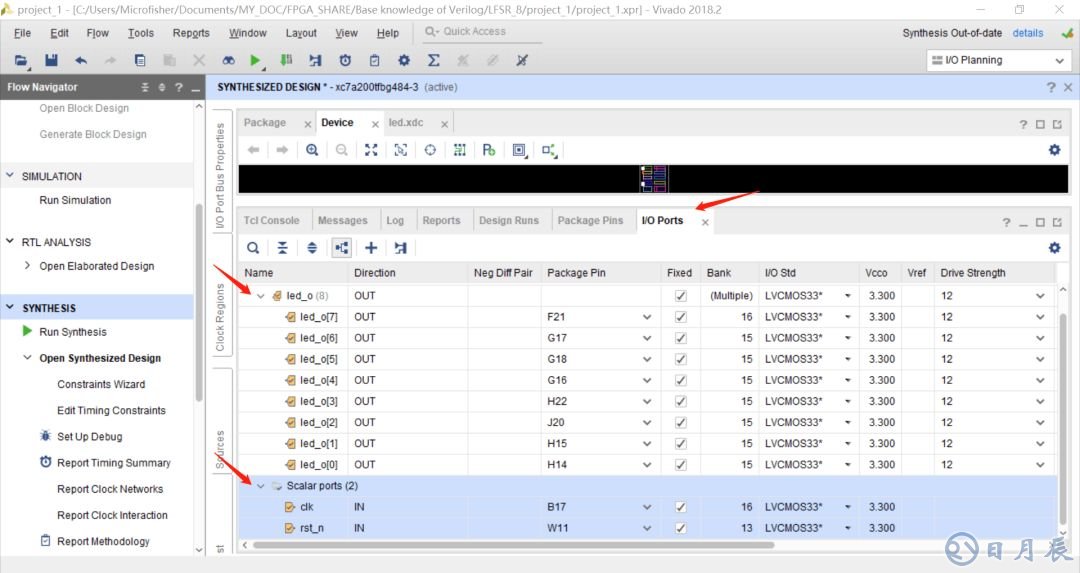

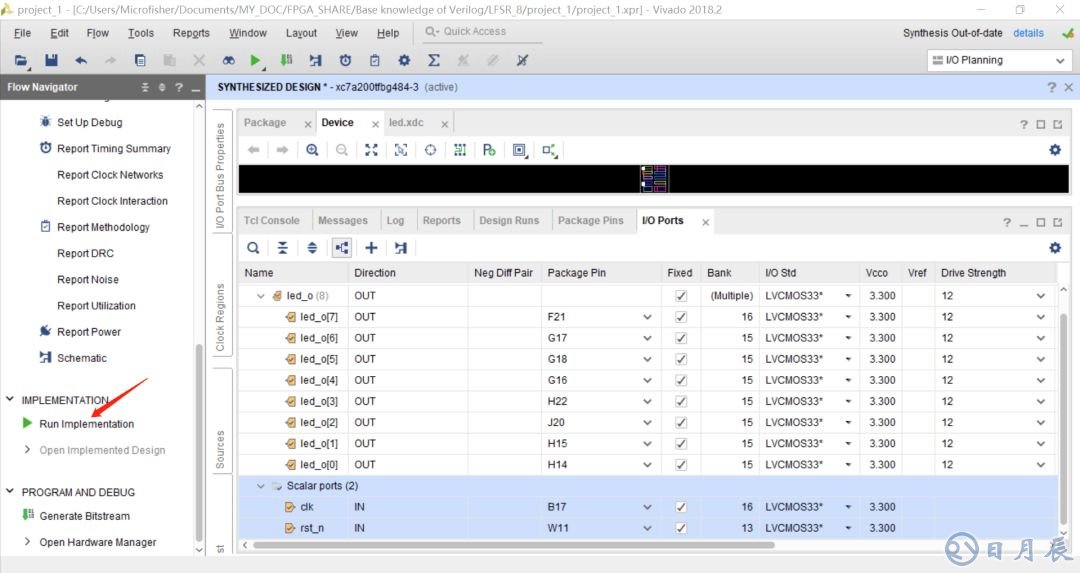

1. Synthesis結(jié)束之后,并且Open Synthesized Design之后。在界面右上角選擇I/O Planning

2. 之后在I/O Ports給I/O端口分配引腳。Package Pin就是對應(yīng)的FPGA芯片的引腳。其中clk接外部晶振輸入,rts_n接外部復(fù)位按鈕,led_o接led燈。

(七)Implementation(實現(xiàn))

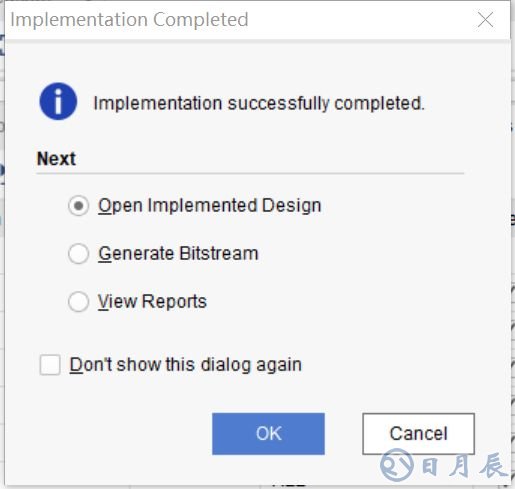

引腳分配完畢之后,在Flow Navigator界面下點擊Run Implementation

Implementation完畢之后會出現(xiàn)如下彈框。點擊OK則會打開Implementation之后的設(shè)計。

對于Implementation的其它一些設(shè)置選項等等,大家可以參考官網(wǎng)文檔 "Vivado Design Suite User Guide: Implementation (UG904)"。

(八) 生成編程文件,上板測試

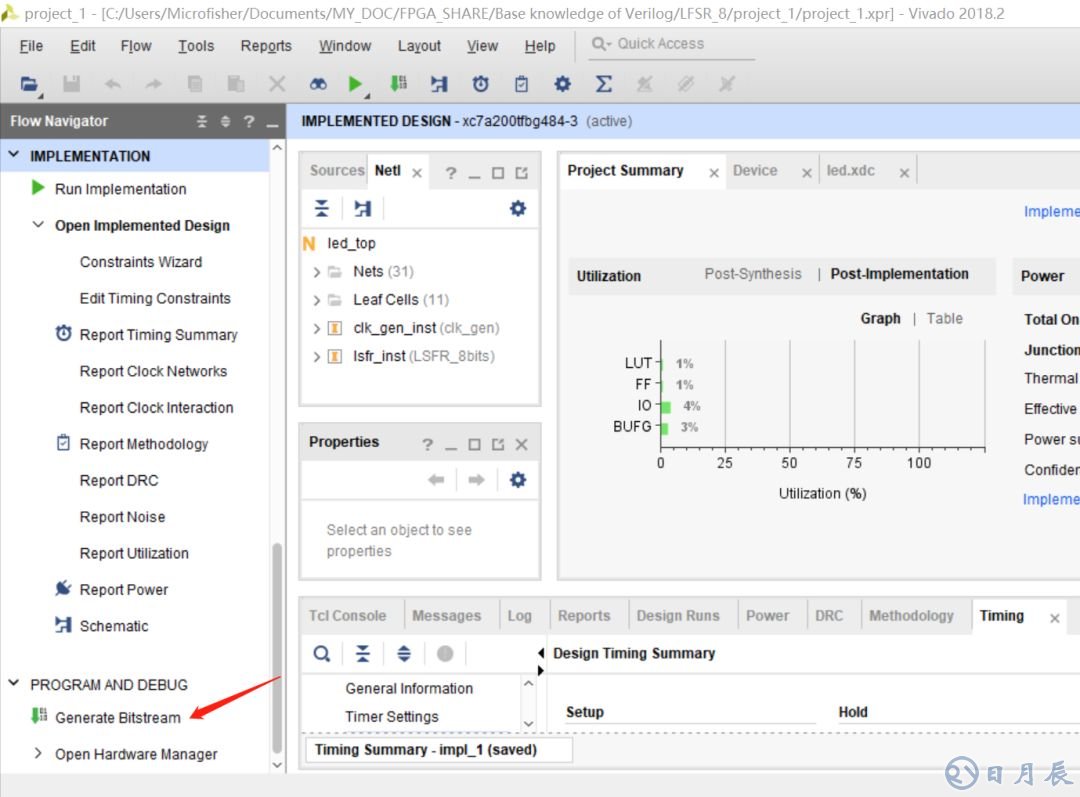

Implementation之后在Flow Navigator界面下點擊Generate Bitstream

默認(rèn)生成的為.bit文件。對于這一塊的其他一些設(shè)置大家可以參考官網(wǎng)資料 “Vivado Design Suite User Guide: Programming and Debugging (UG908)”。

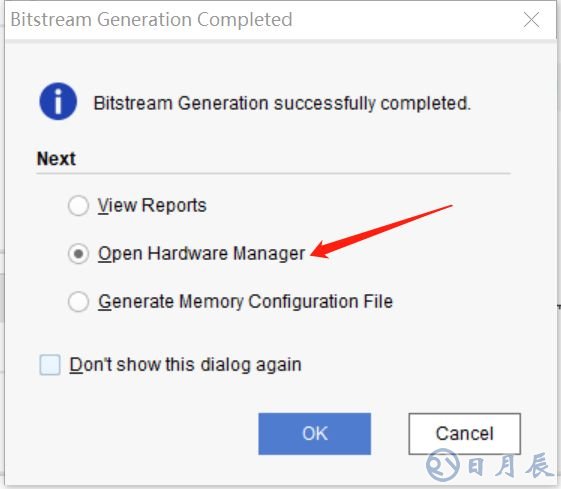

Bitstream文件生成完畢之后,出現(xiàn)如下彈框。接下來選擇Open Hardware Manager,點擊OK。準(zhǔn)備上班測試。

有些開發(fā)板支持SD配置,則直接將生成的.bit文件拷到對應(yīng)的SD卡里面即可。

如果有Xilinx下載器,將Xilinx下載器,開發(fā)板子,電腦連接好,并上電。

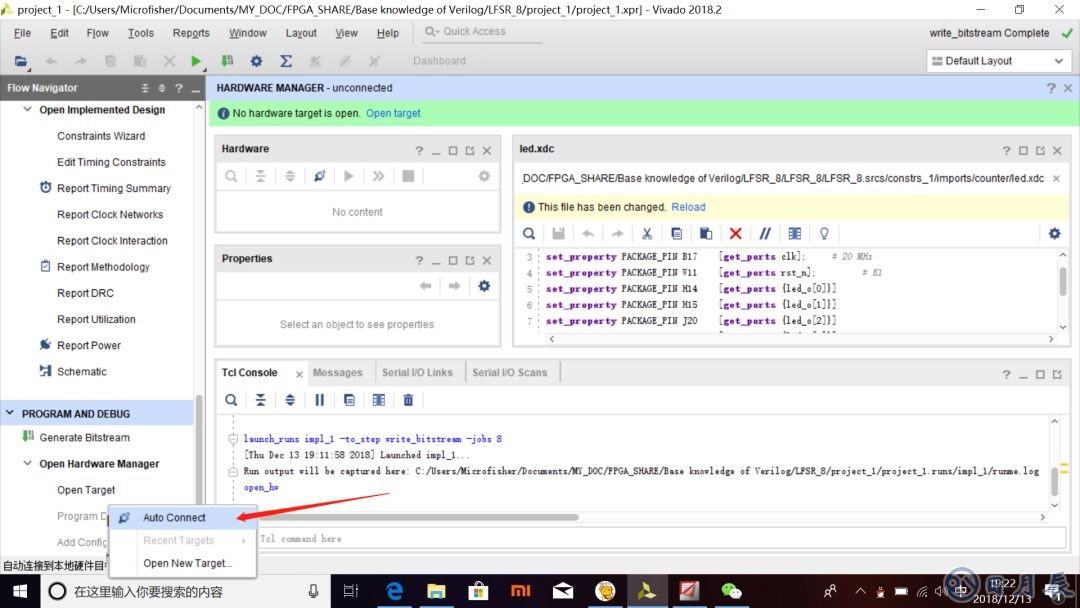

如下所示,點擊Open Target -> Auto Connect

工具自動搜索已連接的器件。一般第一次會連接失敗,出現(xiàn)如下圖所示情況。右擊紅色箭頭所指,再點擊Close Server。

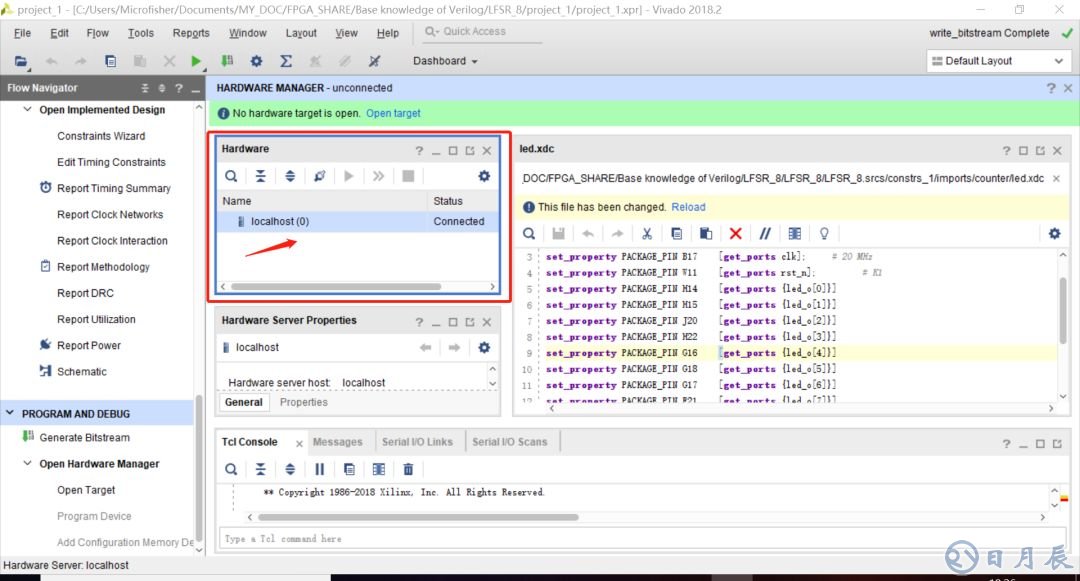

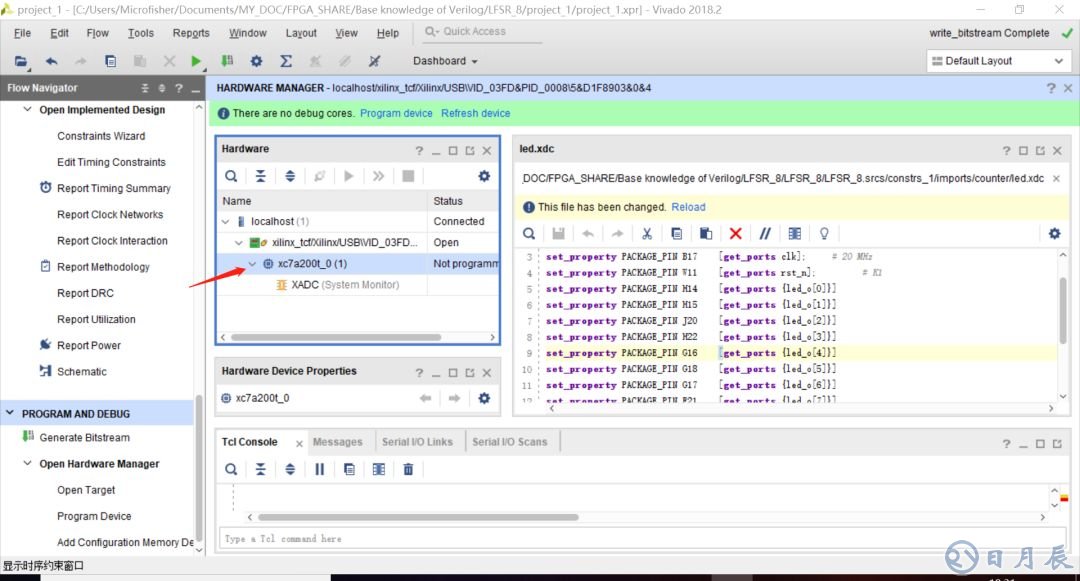

之后再重復(fù)Open Target -> Auto Connect操作,如果連接成功,視圖如下。右擊紅色箭頭所指的器件名,選擇Program Device

然后彈出如下所示框,其自動為我們選擇了剛剛生成的bit文件,點擊Program,工具就會將我們的bit文件配置到FPGA里面去。配置完成板子上就會出現(xiàn)相應(yīng)的效果。

總結(jié)

上述就是一個基本的Vivado使用過程,在這個過程中的每一步,都有相應(yīng)的官網(wǎng)資料推薦,如果大家想要深入了解Vivado具有的強(qiáng)大功能,最好需要去看看這些文檔。

<b id="0toem"><menuitem id="0toem"></menuitem></b>

<code id="0toem"><abbr id="0toem"></abbr></code>

<code id="0toem"></code>